ミニマルファブの2024年版コンテストが変更されました

下記のような形となります。

簡単にまとめると「相当のガチ回路を作らないと箸にも棒にもかからない」という感じのようです。

ですので、腕に覚えのある方は、ぜひ、挑戦してみてもらえればと思います!

- ウェハー試作に採用する作品数は、第1部と第2部の合計で、11個(元々は、25個だった)

- 論文レベルの厳しい評価軸に変更された(今までは実質的になかった)

評価軸内容

第1部の審査は、以下を考慮し総合点で評価します:

1.コンセプト・アイデアの面白さ(考え方のベースや方向性)

2.回路設計の完成度(回路図を作成しているか?)

3.回路検証の実施(SPICEシミュレーションにより動作確認しているか?)

4.レイアウト設計(アレイ素子を有効利用できるよう配線しているか?)

5.レイアウト検証(DRCとLVSを実施しているか?)

6.回路の新規性(ミニマルファブとしてみた場合、新規性のある回路か?)

7.PDKの利用レベル(SPICE、DRC、LVS、PCELLすべてのPDKを使っているか?)

8.設計レポートの完成度(設計結果の報告内容は十分であるか?)

9.動作する可能性(実際にウエハ試作して動作する可能性は?)

10.使用素子数(トランジスタ、抵抗、容量の使用素子数)

第2部:下地からの設計

第1部の評価基準に加え、以下を評価します。

1.回路の斬新さ(ミニマルファブの立場から、回路の新規性)

2.評価の容易性(5ピンで評価できるか)

3.IPとしての可能性(ミニマルファブのIPとしての有用性)

次に、ウェーハ製造に採用するかの判断は、以下も考慮します:

1.5ピンのオンウェーハ測定で、意味のある評価ができるか。

2.評価のためのプログラムが用意されているか(特にAnalog Discovery 2を使った測定)。

3.実測データがあれば、オープンハードウェアとして価値があがるか。

ミニマルファブの2024年版コンテスト

ミニマルファブの2024年版コンテストが開始されました!

第一部募集要項

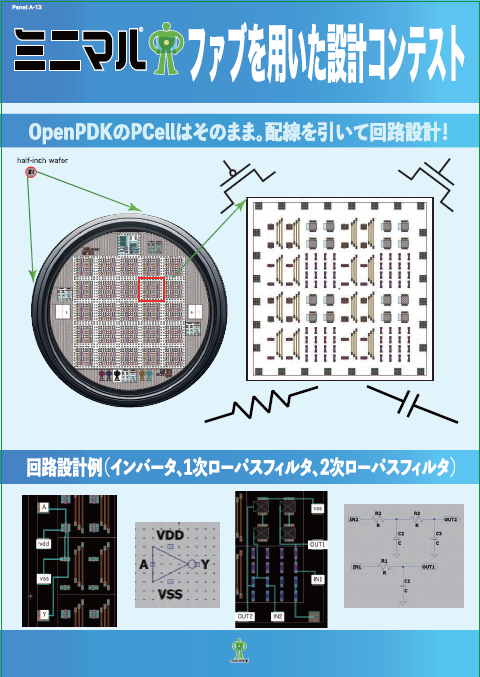

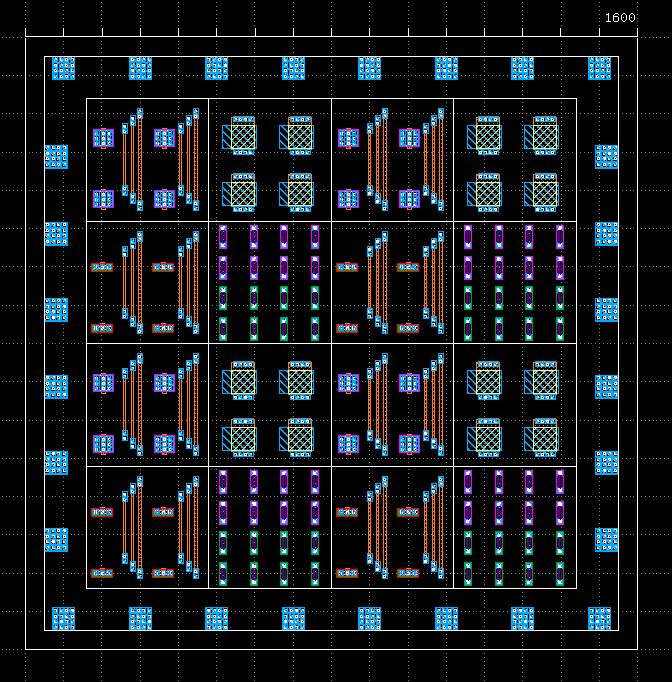

第1部は、昨年と同じ素子アレイをメタル配線して回路を構成するものです。

詳細条件

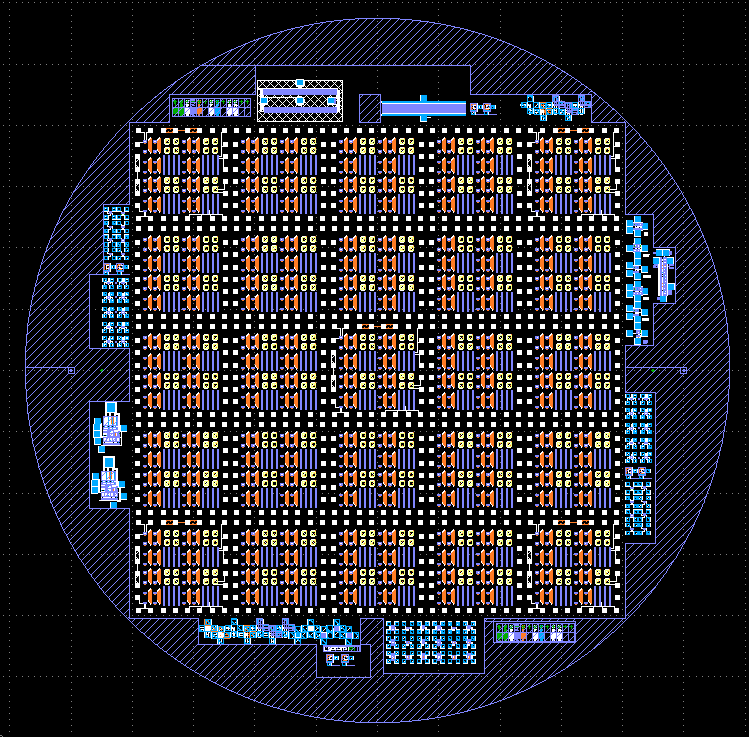

0.5インチのウェーハに、1.6mm角の素子アレーが用意されており、それらをML1のみで配線することで目的に機能を作るというものです。

用意されている素子は、下記の通りとなります。

- NMOS: 16個 (W/L=10um/10um)

- PMOS: 16個 (W/L=40um/10um)

- n拡散抵抗:16本 540 Ω

- p拡散抵抗:16本 3.6 KΩ

-

キャパシタ: 16個 0.41 pF

選定条件

1ウェハを25区画に分ける関係で、エントリーが25区画を超える場合、審査基準にしたがって事前審査し、ミニマルファブの立場から評価の高いものが採用となります。

第二部募集要項

第2部は、素子アレイのチップと同じ面積(1.6mm角)を自由に使っていただくものです。

共通要項

- 製造数は第一部15枚程度、第二部10枚程度(状況により変動あり)

- 設計データは公開する必要がある。

申込み方法

下記のファイル一式をミニマルファブのDiscord「Contest 2024」チャンネルに提出するか、githubで公開してURLを「Contest 2024」チャンネルへ連絡することで申し込みとなります。

- 出来上がったGDS

- シミュレーションに使った回路データ

締め切り

エントリ締め切りは、第1部、第2部ともに、2025年1月6日の23:59です。

環境構築

公式からはPDKのインストール方のみがアナウンスされています。

そこで、ISHI会でWSL/Ubuntu22.04/Mac Appleシリコンシリーズに対応したEDA(開発環境)まで対応した開発環境構築用のスクリプトを作りました。

必要な方はご活用ください。

各環境にて下記のコマンドで環境構築が可能です。

git clone https://github.com/ishi-kai/OpenRule1umPDK_setupEDA

cd OpenRule1umPDK_setupEDA

./eda-setup.sh

./pdk_MF20-setup.sh