# CPUの気持ちを理解しよう！

ISHI会

<https://ishi-kai.org/>

Mail: [info@ishi-kai.org](mailto:info@ishi-kai.org)

とげとげP

# トランジスタ もっとCPUの気持ちが 知りたいですか？

著書 出村成和

とげとげP

# |ISHI|会 = オープンソース半導体 コミュニティー

- メンバー数

- 550名Over (20-30名ほど常にアクティブ)

- ホームページ

- <https://ishi-kai.org/>

- Discord上で活動中

- <https://discord.gg/RwAWF5mZSR>

- イベント告知 (勉強会など)

- <https://ishikai.connpass.com/>

- 20~50名ほどが常時参加

# 論理合成

HDL

デジタル回路

論理合成のイメージ

論理合成

HDL（ハードウェア記述言語）で

記述して、論理回路（RTL）にする

論理回路（ゲート回路）

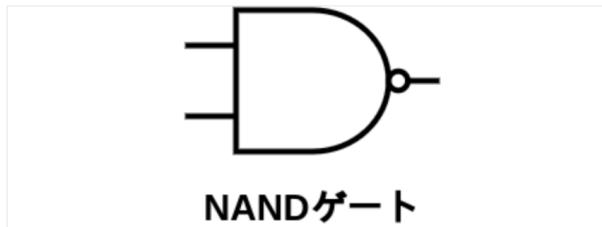

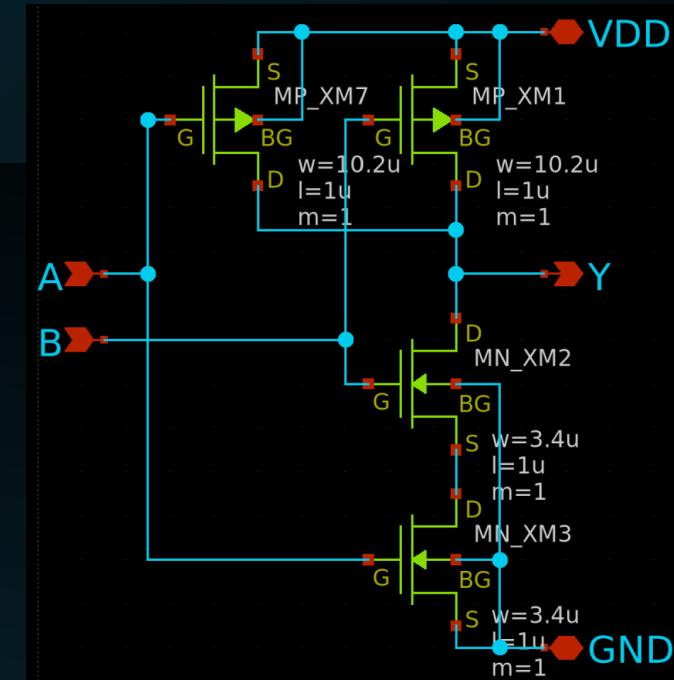

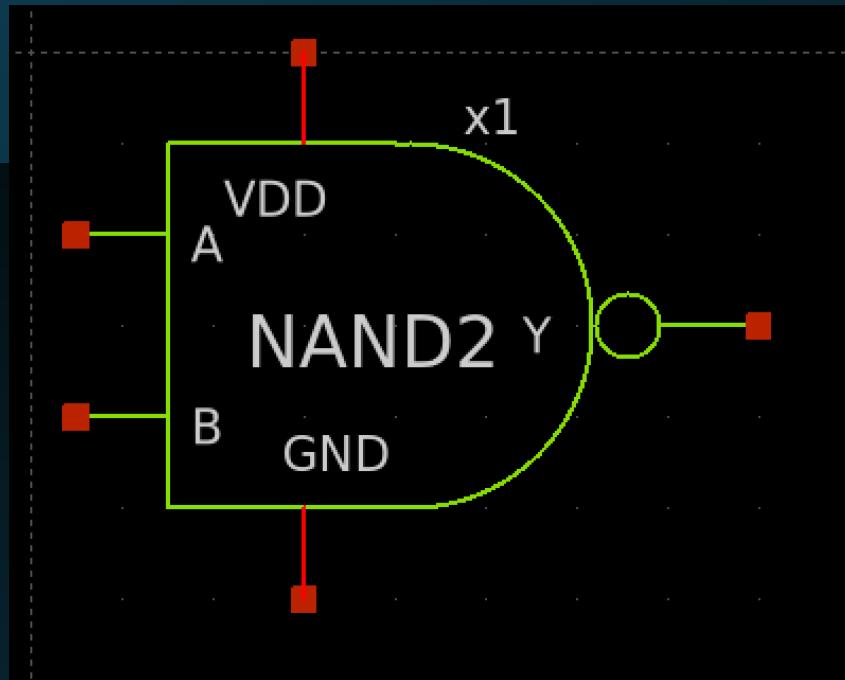

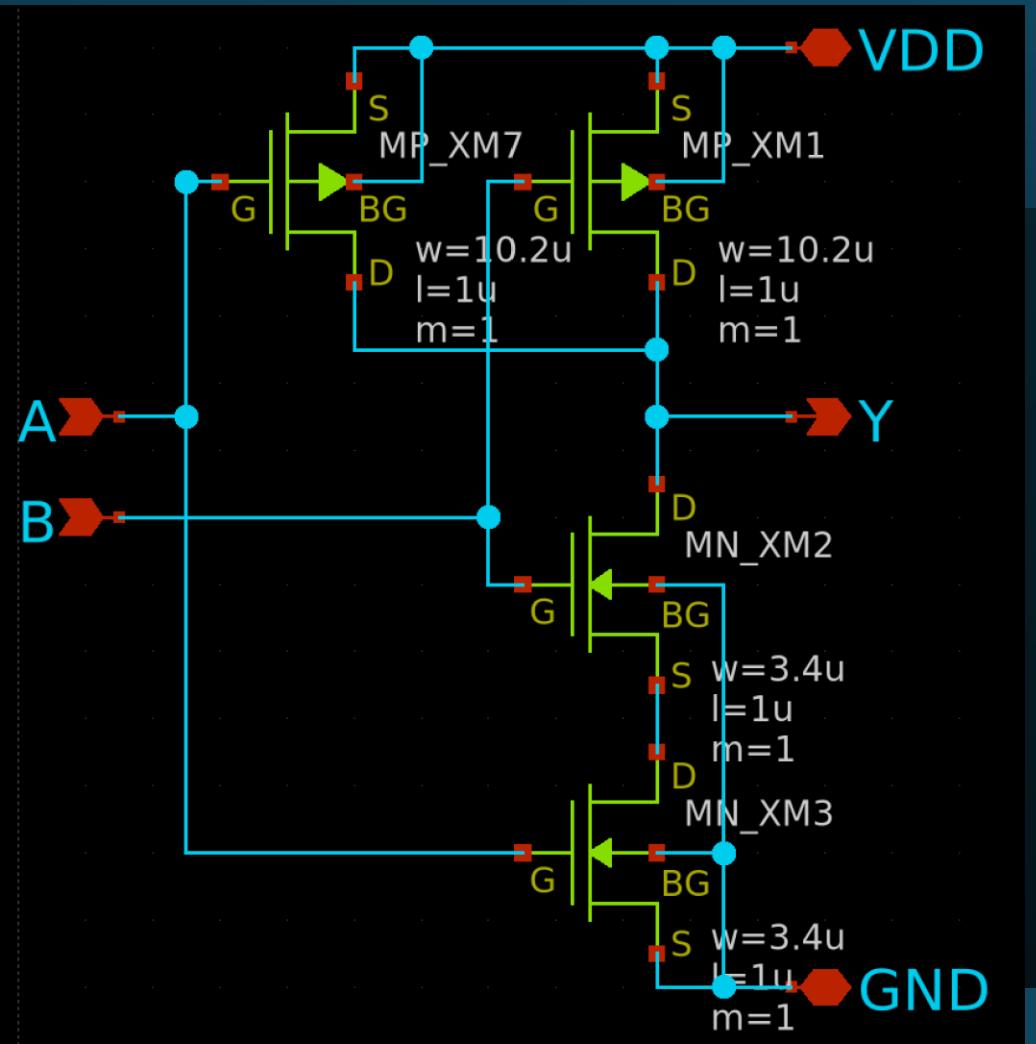

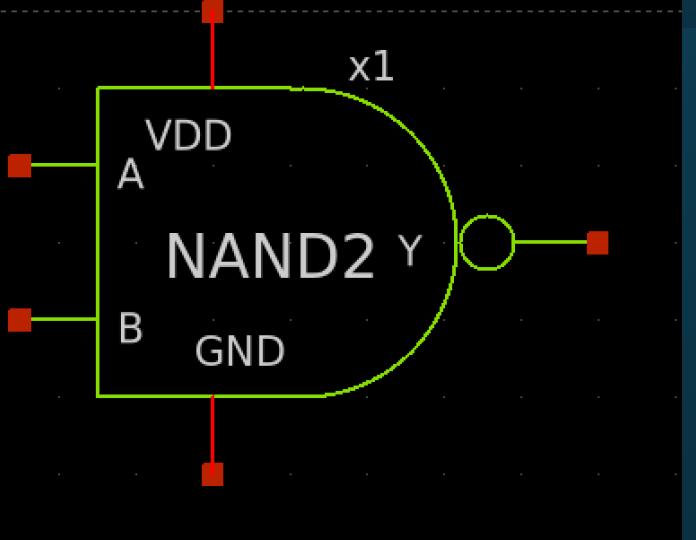

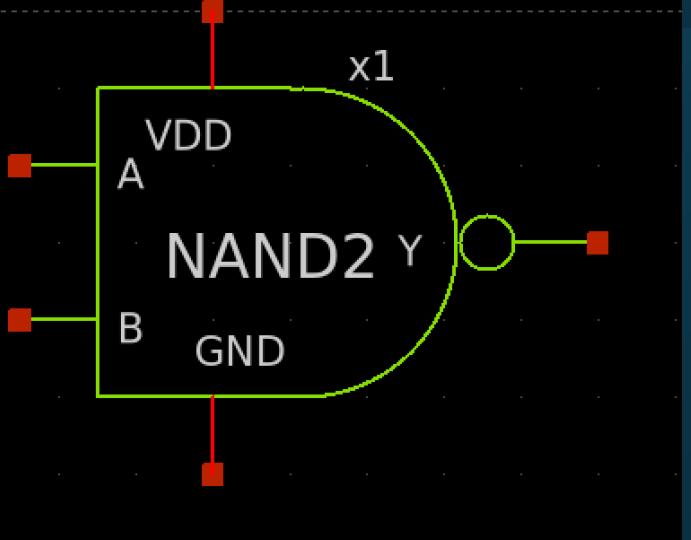

## NAND

次はNANDゲート、これはANDゲートの出力にNOTしたものです、入力の少なくともどちらか一方が0なら1を出力します。それ以外なら0を出力します。

真理値表は以下の通りです。

| A | B | A AND B |

|---|---|---------|

| 0 | 0 | 1       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

NANDゲートの真理値表

Verilogでは、NANDはNOTゲートとANDゲートを組み合わせて~(信号名1 & 信号名2)で表せます。カッコ()は数式と同じく優先順位を表しており、カッコの中身が優先され先に実行されます。少し難易度が上がりましたかね？実際に使ってみましょう。

Basic.vのassign文の部分を編集し、ANDゲートをNANDゲートに変更します。

```

assign w_x = ~(r_a & r_b);

```

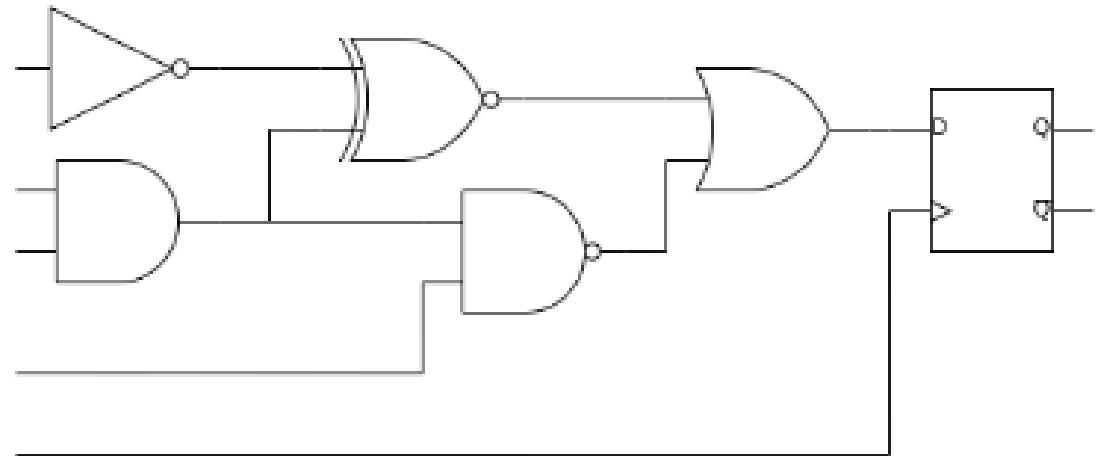

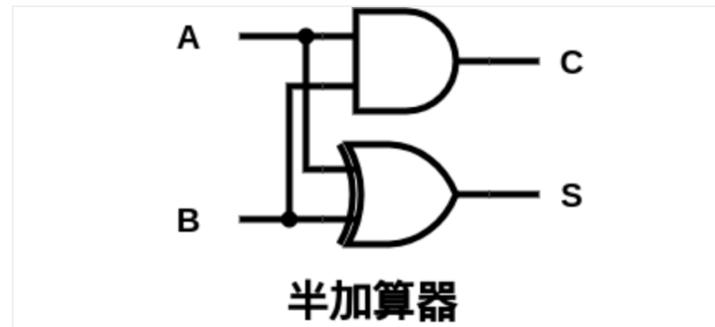

## HalfAdder

次はデジタル回路で少し面白い回路を紹介します。HalfAdder、半加算器です。以下のANDとXORで構成された回路を見てください。

この回路の真理値表を書いてみましょう。以下の通りです。

| A | B | C | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

CがAND回路の出力でSがXOR回路の出力になっています。当然っちゃ当然ですね。ですがよく見てください、このCとS、AとBの二進数の加算結果の二桁目と一桁目になっていますね。ちなみにCは繰り上がりを意味するCarryの略で、Sは和を意味するSumの略です、

論理回路（中身）

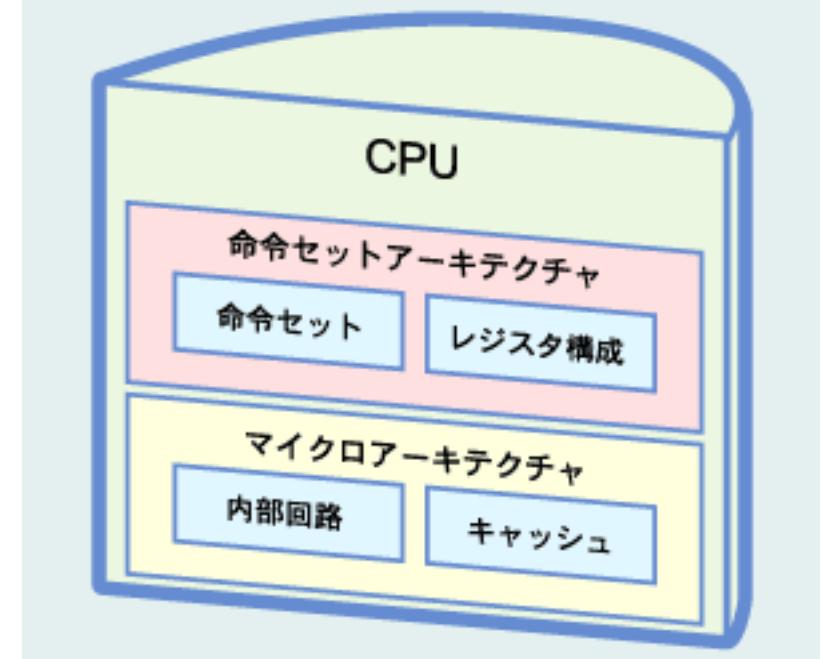

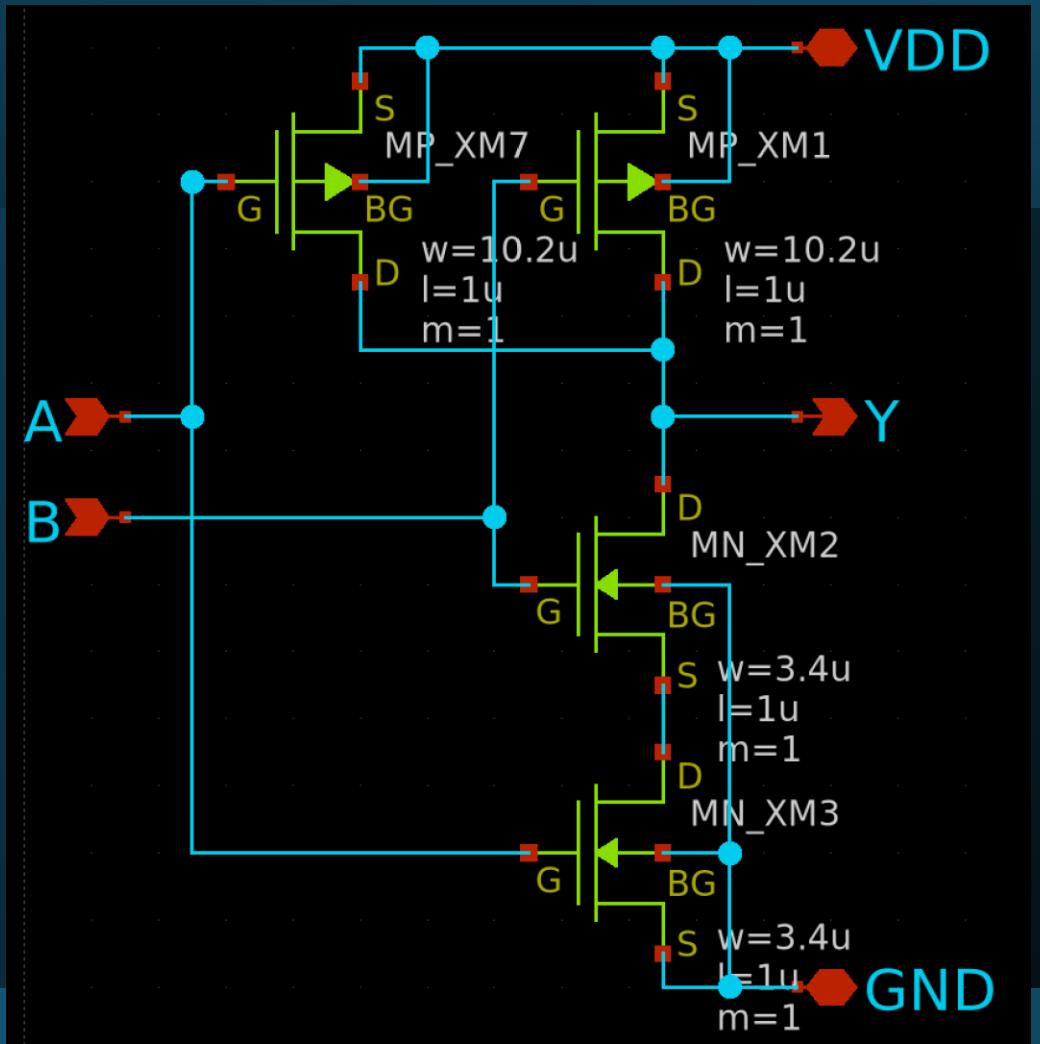

# 論理回路の正体

中身はP-FETとN-FET

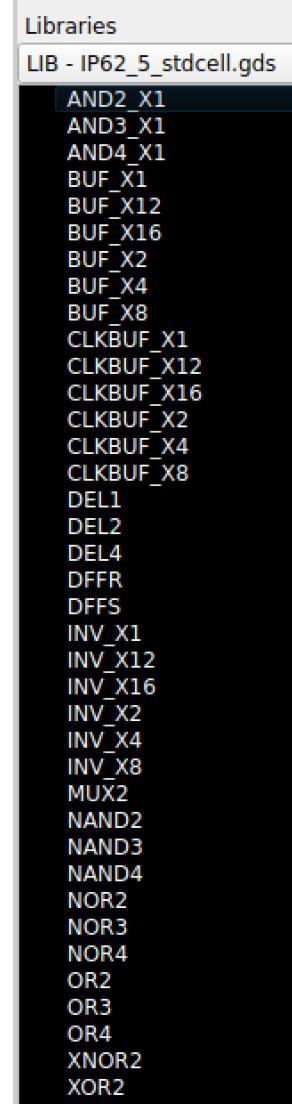

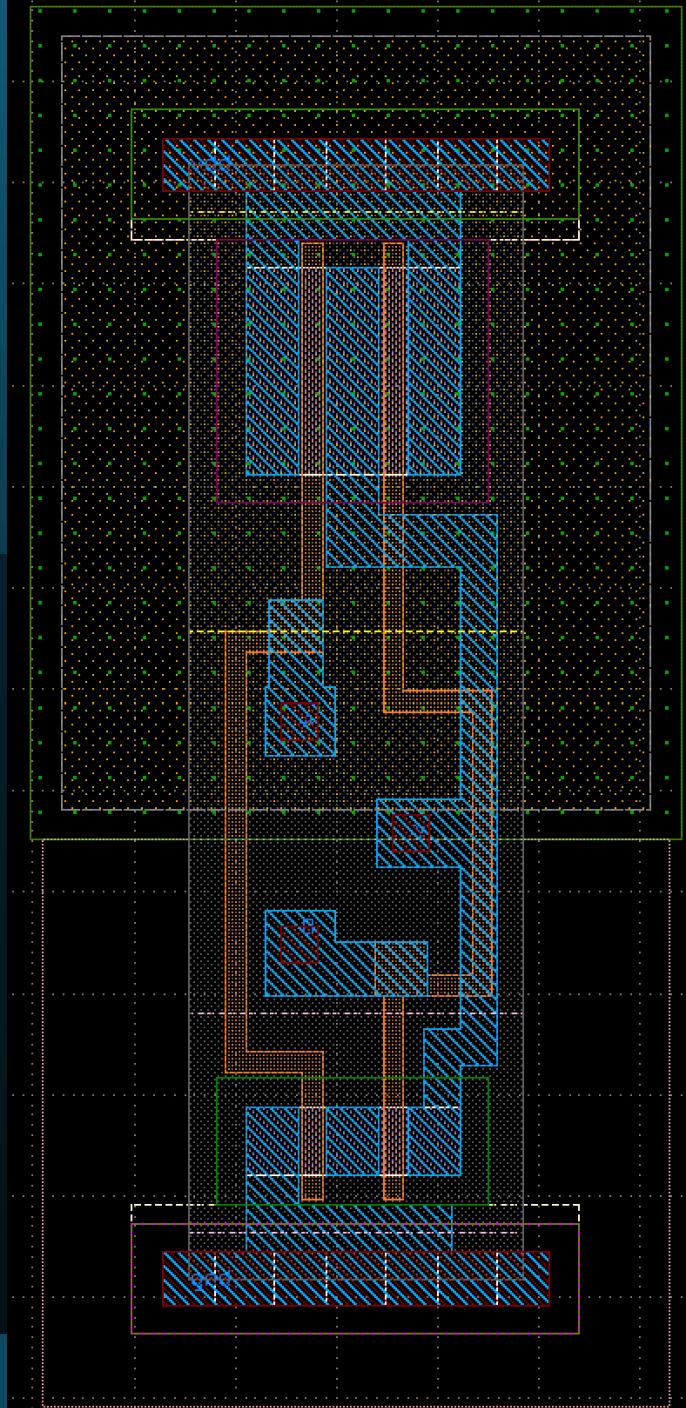

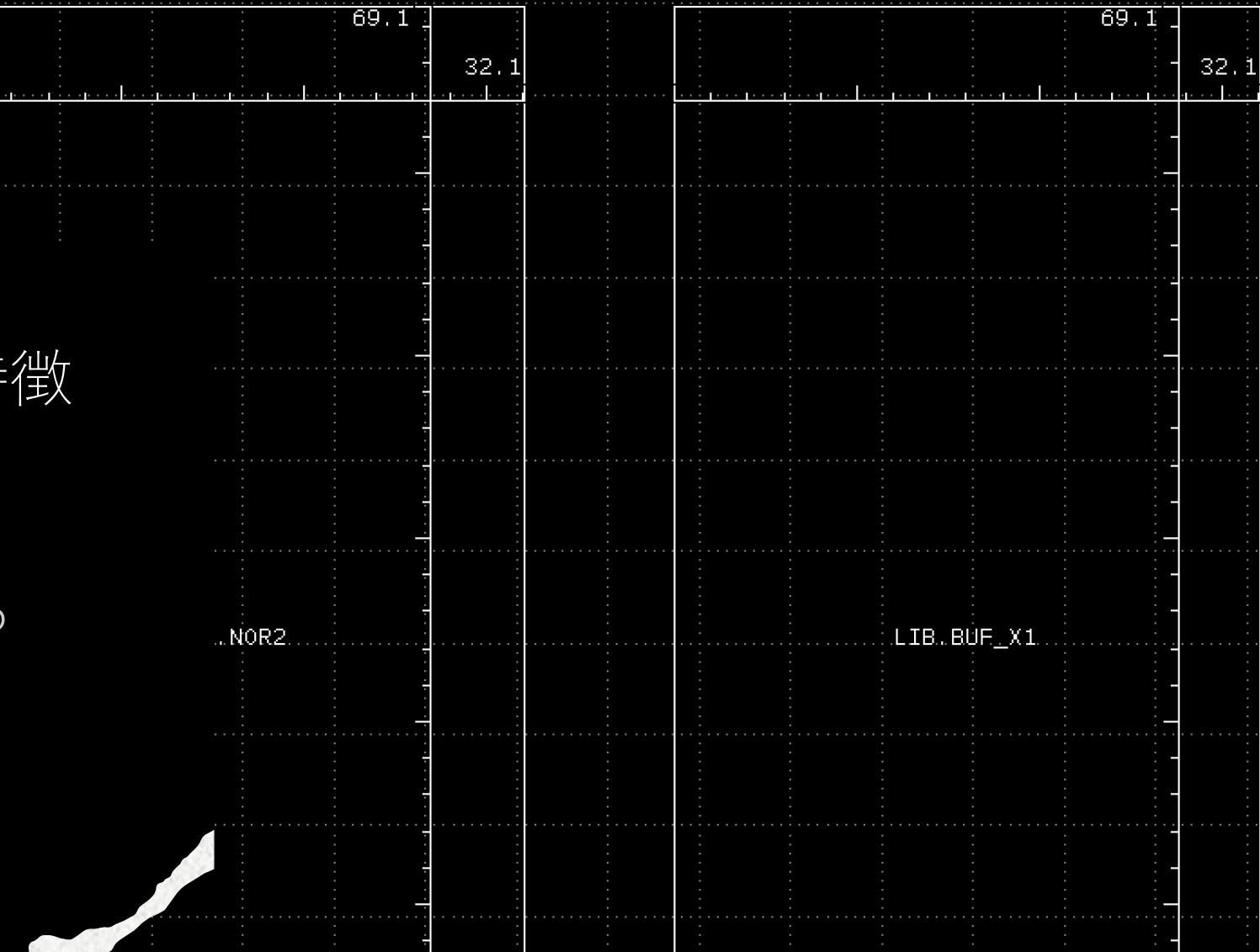

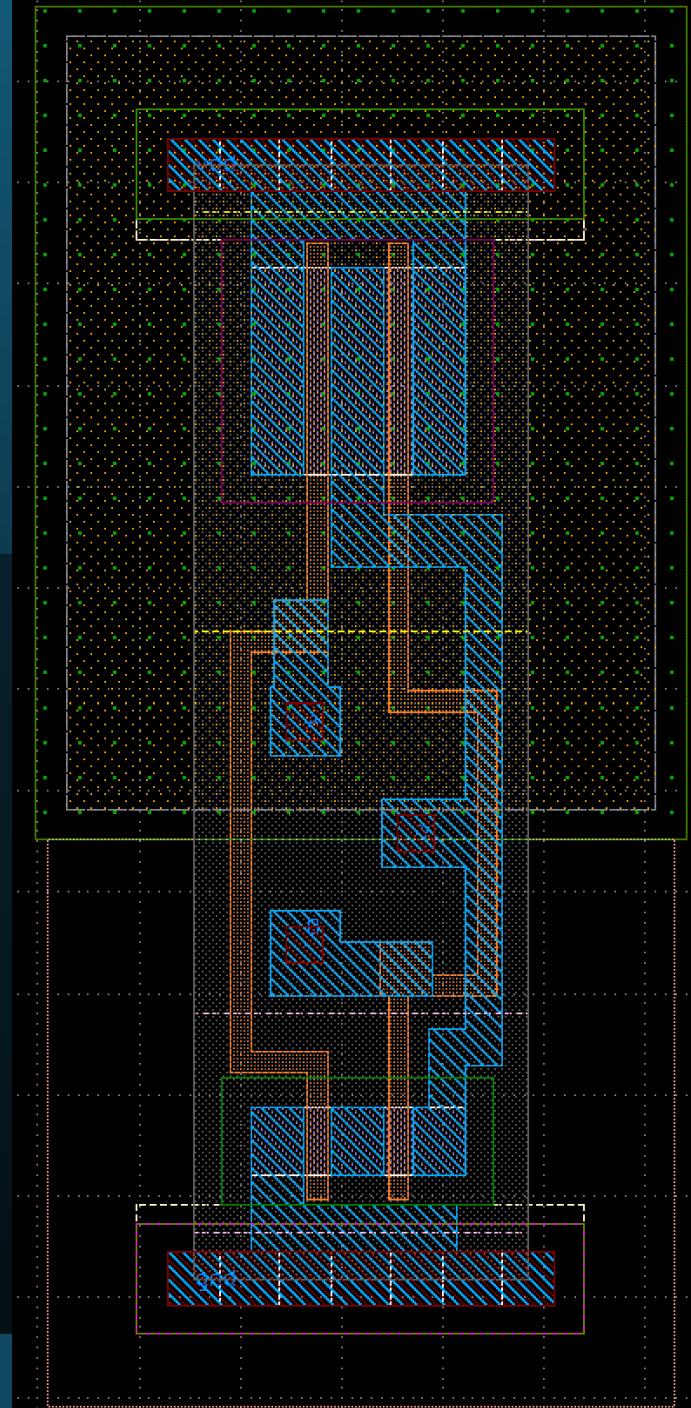

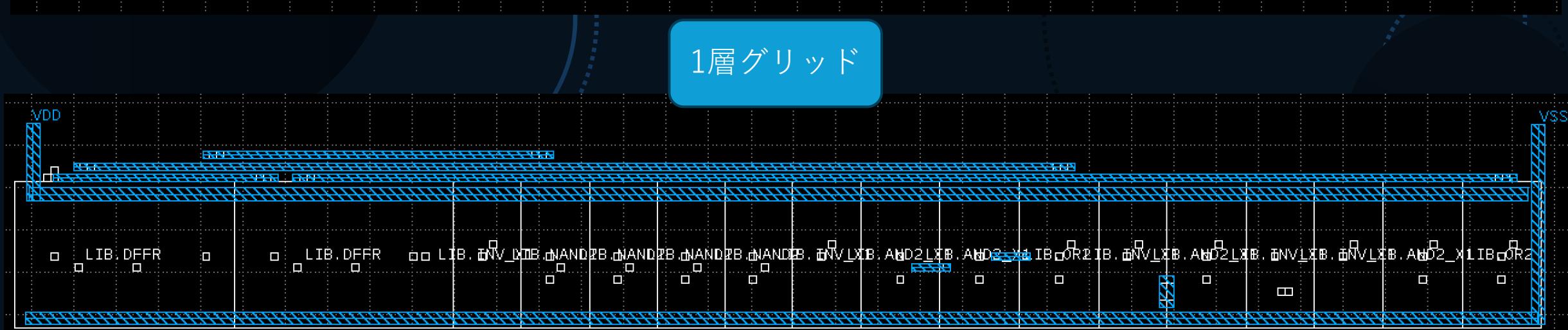

# スタンダードドセル

## スタンダードセルの特徴

- 縦の長さは均一

- 横の長さが何種類がある

LIB.DFFR LIB.DFFR LIB.INV\_X1B.NAND2B.NAND2B.NANDB.INV\_LXB.AND2LXB.AND2\_X1IB.OR2IB.INVLXB.AND2LXB.INVXB.INVLB.AND2\_X1IB.QR2

VDD ライン

P-FET

Sが共通

## スタンダードセルの特徴

- ・ 上がP-FET, 下がN-FET

- ・ VDDとVSSラインがある

- ・ ポートは何種類がある

VSS ライン

N-FET

Sが共通

ピン

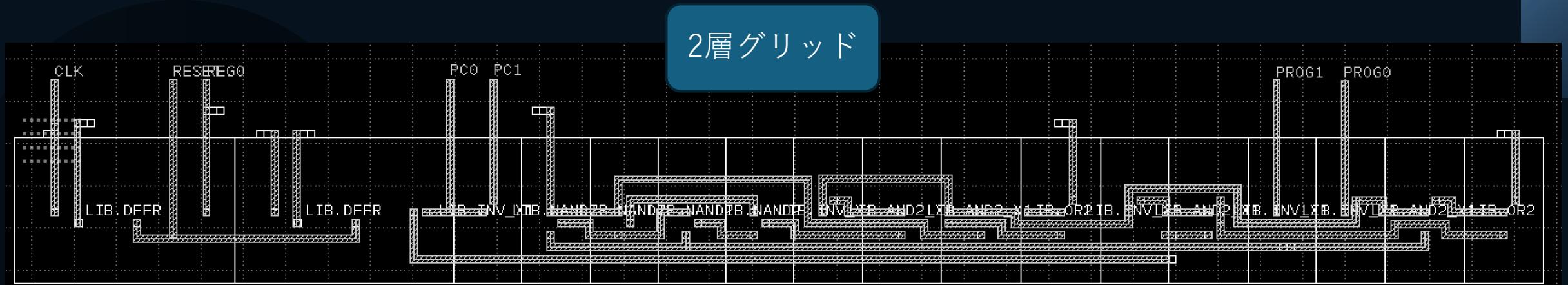

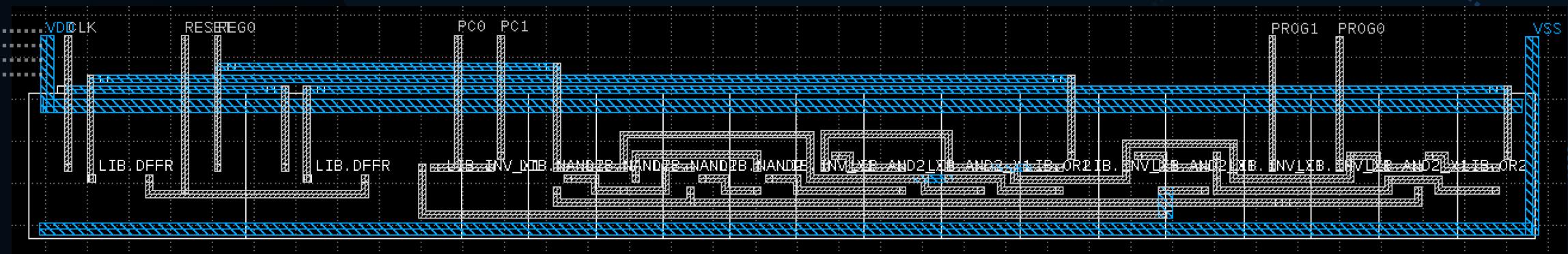

# スタンダードドセル

P&R (配置配線)

# グリッド配線 (電源グリッド)

- メタル層を縦と横で分ける

- 6層などある場合は6層、5層をVDD, VSSに割り当てる→電源グリッドと呼ばれる

- 理由：上部の層の方が線厚が厚いため

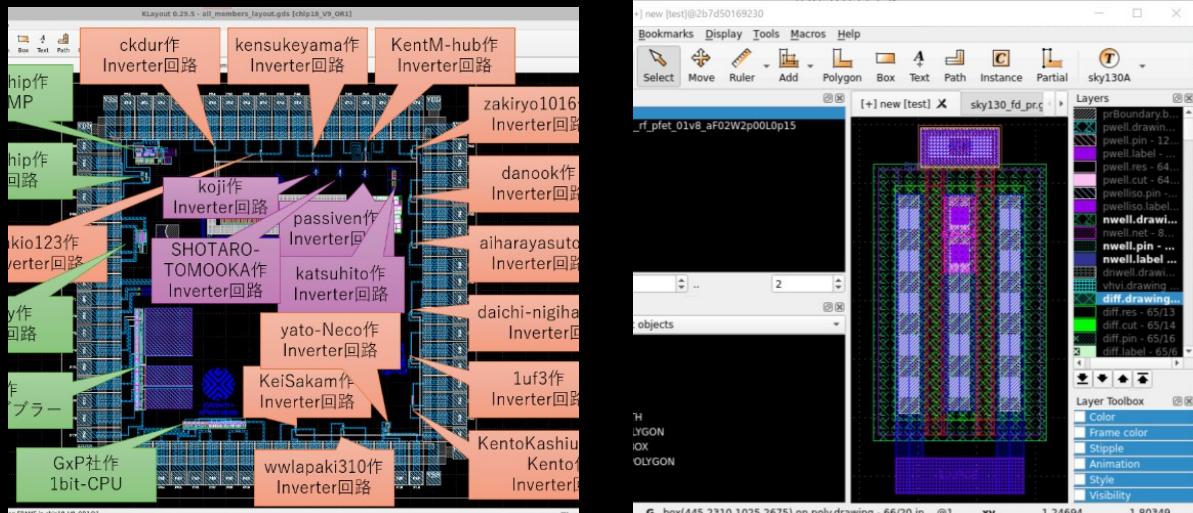

# 完成図

# ハンズオンセミナー

# ハンズオン セミナー

- 知識ゼロから半導体設計の基礎がすべて学べる！

一番簡単なインバーター回路のハンズオンセミナー

- Xschemによる回路設計

- トランジスタの組み合わせで機能を実現する作業

- ngspiceによる回路特性シミュレーション

- 上記の回路が正しく動作するかを検証する作業

- klayoutによる回路デザイン

- トランジスタを実際の半導体の上に配置する作業

- 丸々1日の講習会となります

- 講習会実施実績

- <https://ishikai.connpass.com/event/303102/>

- [https://www.noritsuna.jp/download/ishi\\_20231110\\_3\\_zki\\_ver2.pdf](https://www.noritsuna.jp/download/ishi_20231110_3_zki_ver2.pdf)

- 参加者の声（半導体設計未経験者。電子工作をしたことがあるレベル）

- チップの設計体験によりすごく技術的な刺激を受けた

- 半導体は全く未知のものだったが理解できたことで新しい知見を得ることが出来た

# |SHI|会の情報

- メンバー数

- 550名Over (20-30名ほど常にアクティブ)

- ホームページ

- <https://ishi-kai.org/>

- Discord上で活動中

- <https://discord.gg/RwAWF5mZSR>

- イベント告知（勉強会など）

- <https://ishikai.connpass.com/>

- 20～50名ほどが常時参加